Follower Of All Or Turn Nyt Crossword Clue

Here are some of the images for Follower Of All Or Turn Nyt Crossword Clue that we found in our website database.

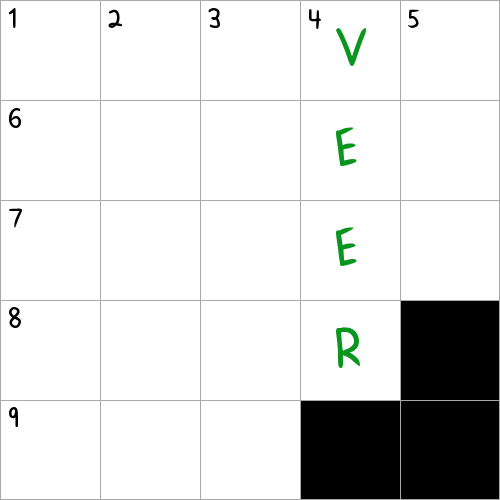

#39 Make a sudden turn #39 NYT Mini Crossword puzzle clue answer and hints

quot Meenie miney quot follower NYT Crossword

Mars follower in Marseille Crossword Clue NYT Crossword Answers

Make a sudden turn NYT crossword clue NY Times Puzzles

Make a sudden turn NYT Crossword Clue November 18 2024

Romeo follower Crossword Clue Answers Crossword Solver

Sigma follower NYT Crossword Clue

Website that competes with PCMag NYT Crossword December 7 2025

#39 Make a sudden turn #39 NYT Mini Crossword puzzle clue answer and hints

Have the Final Turn NYT Crossword Power Up Gaming

Have the Final Turn NYT Crossword Power Up Gaming

Rex Parker Does the NYT Crossword Puzzle: Turn follower in Texas Hold

Rex Parker Does the NYT Crossword Puzzle: Turn follower in Texas Hold

Days Of Olden Times Crossword prntbl concejomunicipaldechinu gov co

Pikachu Coloring Pages Printable prntbl concejomunicipaldechinu gov co

Pikachu Coloring Pages Printable prntbl concejomunicipaldechinu gov co

Pikachu Coloring Pages Printable prntbl concejomunicipaldechinu gov co

Rex Parker Does the NYT Crossword Puzzle: Valley where David fought

Rex Parker Does the NYT Crossword Puzzle: Seneca Falls orator Lucretia